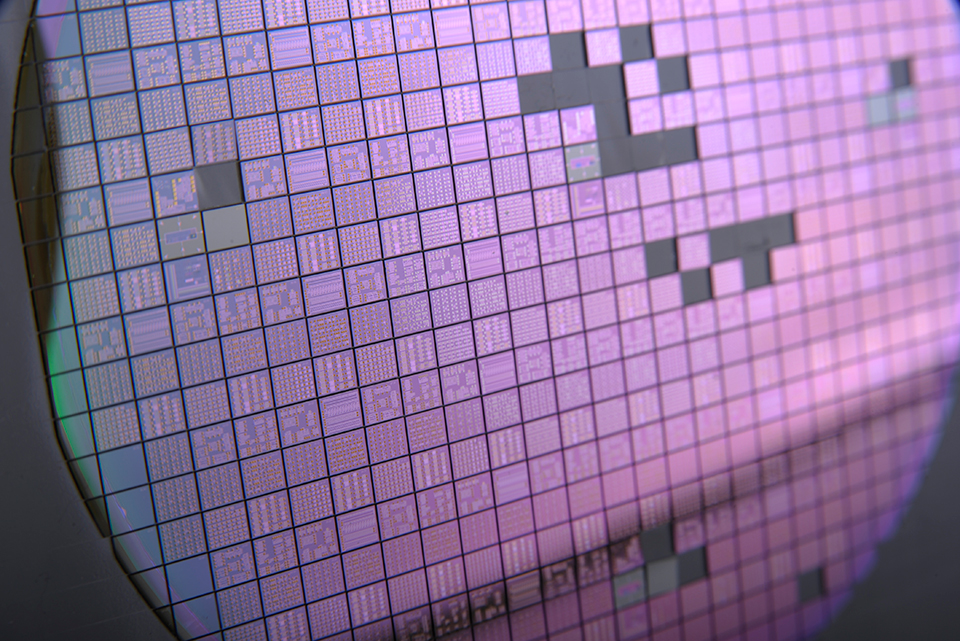

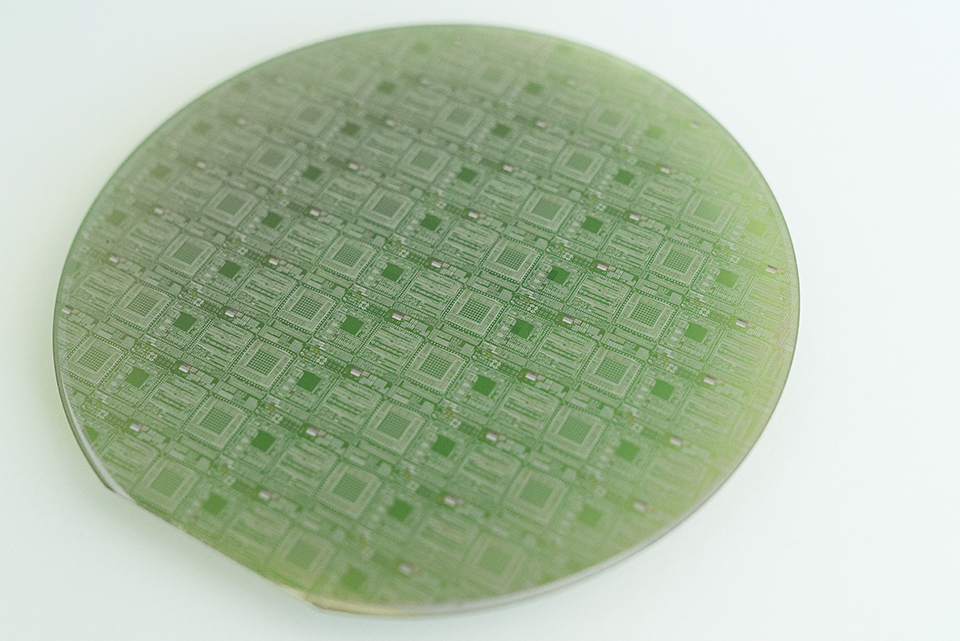

Within EUROPRACTICE, Fraunhofer IISB offers early-access to its 2µm SiC CMOS technology including NMOS and PMOS transistors as well as passive components and pn-diodes for integrated circuits. These circuits are capable of operating at temperatures above 300 °C (up to approx. 600 °C). Additional process modules are available for high-voltage devices, isolated transistors and SiC device templates exceeding CMOS circuits.

The targeted applications for this technology include integrated circuits beyond silicon for extremely harsh environments including high temperatures and radiation levels with low leakage. Additionally, the technology can be tailored to obtain specialized optical SiC devices and quantum sensor templates.

Fraunhofer Institute for Integrated Systems and Device Technology IISB

Fraunhofer Institute for Integrated Systems and Device Technology IISB